# Survey of Research Projects Conducted by Sasao's Group (FY2013-FY2020).

Tsutomu Sasao Meiji University, Kawasaki 214-8571, Japan December 20, 2020

Abstract—This paper surveys research projects conducted by Prof. Tsutomu Sasao's group from FY2013 to FY2020, at Meiji University. Research projects in this period can be divided into the following groups: 1) Index generation functions; 2) Classification functions; 3) Decomposition of functions; 4) Fast sequential circuits to evaluate decision diagrams; 5) Special circuits; 6) Decision diagrams; 7) History of logic design; 8) CAM optimization; 9) IC design tools; 10) Interconnection circuits; 11) EXOR logic synthesis; 12) Systems analysis using multi-valued decision diagrams; 13) Testable functions; 15) Miscellaneous Projects

#### I. Projects

#### A. Index Generation Functions

An index generation functions is a mapping:

$$f: D \to \{1, 2, \dots, k\},\$$

where  $D \subset B^n$ ,  $B = \{0,1\}$ , |D| = k, that is f is defined only for k combinations,

Sasao conceived of the concept of index generation functions in 2008. It a mathematical model of a content addressable memory (CAM). CAMs are used for pattern matching, but they are expensive and dissipate high power. Sasao invented a circuit that performs the CAM operation using conventional memories and a small amount of glue logic. To implement index generation functions compactly, he developed various synthesis techniques [18], [42], [46], [60], [69], and [86].

# B. Classification Functions

A classification function is a generalization of an index generation function. It is useful for data-mining and machine learning. [89] considered hand-written character recognition. [87] showed a method to reduce the number of variables. [77] and [78] considered multi-valued input decision functions representing mushrooms, breast cancer and hepatitis. After moving to Meiji, Sasao shifted his research from logic design to data mining. This project has been selected as a JSPS grant for FY2020 to FY2022. Also, [78] was awarded a distinctive contributed paper award at ISMVL-2020.

# C. Decomposition of Functions

We considered three types of decompositions for index generation functions and classification functions.

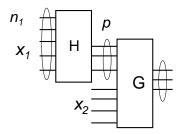

**Functional Decomposition** can be implemented by the circuit shown in Fig. 1.1. Index generation functions with weight k have a decomposition with  $p \leq \lceil \log_2 k \rceil$ , where p denotes the number of connections between H and G.

Fig. 1.1. Functional Decomposition

[52] shows an efficient method to find decompositions. A decomposition is **support-reducing** if  $p < n_1$ , where  $n_1$  is the number of inputs for module H in Fig. 1.1. [55] showed that support-reducing decomposition can be found efficiently for index generation functions. Note that for ordinary logic functions, detection of support-reducing decomposition is very hard. [50] and [63] used a Monte Carlo approach to predict the column multiplicity of decomposition charts for index generation functions.

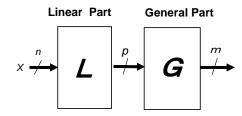

**Linear Decomposition** can be implemented by the circuit shown in Fig. 1.2. When  $k \ll 2^n$ , **linear decompositions** are very effective. That is, index generation functions always have support-reducing disjoint decompositions. We assume that the cost of the linear part is np, while the cost of the general part is  $m2^p$ . Since p, the number of inputs to p is very important, we are interested in the size of p. By experimental results, we conjectured that  $p \le 2\lceil \log_2 k \rceil - 2$ .

Fig. 1.2. Linear Decomposition

We analyzed bounds on p [21], [24], [64], [68].

We developed various algorithms to reduce p, [2], [13], [15], [18], [28], [33], [36], [39], [48], [54], [56], [58], [61], [70], [76].

[90] considered a method to find an exact minimum linear decomposition for symmetric index generation functions. [85] considered irreducible index generation functions, for which no linear decomposition exist. [84] improved an upper bound on the number of variables p to represent index generation functions using linear decompositions. Finally, it was proved that

$$p \leq \lceil 2\log_2 k \rceil - 2.$$

[81] used dynamic programming to find an optimum linear decomposition for index generation functions.

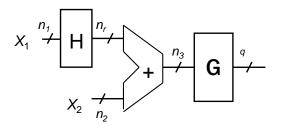

**Row-shift Decomposition** is a new type of decomposition invented by Sasao in 2012. It uses an adder as shown in Fig.1.3. [7] considered cyclic row-shift decompositions. [65]

Fig. 1.3. Row-Shift Decomposition

and [80] analyzed the complexity of row-shift decompositions.

# D. Fast Sequential Circuits to Evaluate Decision Diagrams

To evaluate decision diagrams quickly, various sequential circuits were developed. This project was mainly conducted by Prof. Nakahara. [4], [9], [10], [11], [19], [20], [25], [31], [34], [43], [44], [57].

### E. Special Circuits

[41] and [73] used the Residue Number System (RNS) to implement neural networks. [32], [47] and [53] considered fast FFT circuits.

[6] considered various circuits to quickly generate functions having a certain property, including combinational number systems, permutations, and set partitions. [29] shows a circuit to generate partitions. [45] considered a set partition number system.

## F. Decision Diagrams

One of the most important problems in logic design is to represent logic functions compactly. Zero-suppressed decision diagrams (ZDDs) are such representations. We published an edited book on ZDDs [30].

# G. History of Logic Design

Sasao has been working with logic synthesis for more than 40 years. [1] analyzed highly cited papers on multi-valued logic (MVL). [5] surveyed Sasao's work on logic synthesis. [83] surveyed Sasao's work on EXOR logic synthesis. [75] described the first relay computer developed in Japan. Profs. Goto and Komamiya used various techniques to design an

asynchronous relay computer, which is now displayed at the National Museum of Nature and Science, Tokyo, Japan. [37] summarized the work of Y. Komamiya on the design of arithmetic circuits using EXOR logic gates.

## H. CAM Optimization

A CAM is an important device for packet classification. Since CAMs are expensive and dissipate high power, they should be minimized. This project was related to I. Syafalni's Ph.D thesis.

CAM optimization: [8], [12], [14], [27]. CAM test: [38], [40], [51], [72], [74].

# I. IC Design Tool

This project was mainly conducted by Dr. I. Syafalni, who was working at a system design company in Fukuoka, Japan. The following papers are related to his work. [62], [67].

#### J. Interconnection Network

With Prof. Y. Koga, Sasao developed a design method for multi-terminal universal interconnection networks [88].

# K. EXOR Logic Synthesis

In [71], a design method for multi-output linear circuits is shown. Such circuits are useful in the realization of the linear part of Fig. 1.2. In [59] and [66], methods to identify affine equivalence classes of logic functions are shown. Note that if two functions  $f_1$  and  $f_2$  are affine equivalent, then the two functions can be realized by the same circuit in Fig. 1.2, where G is the same for  $f_1$  and  $f_2$ .

# L. System Analysis using Multi-valued Decision Diagrams

This project was mainly conducted by Prof. S. Nagayama. [3], [16], [22], [26], [35].

#### M. Testable Functions

Consider the class of single-output two-level irredundant AND-OR circuits. Inadmissible classes of functions cannot be caused by stuck-at faults [23], [49]. This project was mainly conducted by Prof. D. K. Das.

# N. Miscellaneous Projects

In addition to the other projects, Sasao performed miscellaneous projects with other researchers:

In [79] and [82], asymmetric logic functions are enumerated. In [91], properties of partition functions are analyzed. In [17], a method to design a numerical function generator is shown.

#### II. RESEARCH GRANTS

During the period from FY2013 to FY2019, Sasao obtained the following grants:

## KAKEN (JSPS)

- "Logic synthesis using linear transformation and memory," (April 2011 to March 2014).

- "Study on the design of fast updatable index generation circuits," (April 2014 to March 2017).

- "Study on decomposition of index generation functions," (April 2017 to March 2020).

- "Study on minimization of variables for classification functions, and their applications," (April 2020 to March 2023).

## A-STEP (JST)

• "Low-power programmable logic circuits for pattern matching," (April 2013 to March 2014).

#### III. BOOKS

During this period, Sasao published two books: One is an edited book related to the Reed-Muller Workshop by Sasao and Butler in 2013. The other is a monograph on index generation functions.

- T. Sasao and J. T. Butler, Applications of Zero-Suppressed Decision Diagrams, Synthesis Lectures on Digital Circuits and Systems, Morgan-Claypool, November 2014, 123 pages.

- T. Sasao, *Index Generation Functions*, Synthesis Lectures on Digital Circuits and Systems, Morgan-Claypool, Oct. 2019, 184 pages.

## IV. PATENT

During the period, Sasao obtained one international patent with the financial support of JST. Title: Content addressable memory, an index generator, and a registered information update method

Patent number: US9865350 Filed: August 19, 2015

Date of Patent: January 9, 2018 Assignee: Meiji University Inventor: Tsutomu Sasao

## V. AWARDS

Sasao's group received many international awards. Major awards include:

- 1) **Outstanding Contributed Paper Award**, (awarded at ISMVL-2013).

- S. Nagayama, T. Sasao, and J. T. Butler, "Analysis of multi-state systems with multi-state components using EVMDDs," *International Symposium on Multiple-Valued Logic* (ISMVL-2012), Victoria, Canada, May 14-16, 2012, pp. 122-127.

- Best Paper Award, (awarded at MCSoc-13).

H. Nakahara, T. Sasao, and M. Matsuura, "A packet classifier using parallel EVMDD(k) machine," 7th IEEE

- International Symposium on Embedded Multicore SoCs (MCSoC-13), Tokyo, Japan, Sept. 26-28, 2013.

- 3) Outstanding Paper Award, (awarded at SASIMI 2013). T. Sasao, Y. Urano, and Y. Iguchi, "A heuristic method to find linear decompositions for incompletely specified index generation functions," The 18th workshop on Synthesis and System Integration of Mixed Information Technologies (SASIMI-2013), Sapporo, Japan, Oct. 21-22, 2013, R3-1, pp. 143-148.

- Best Paper Award, (awarded at IEEE TENCON 2017.)

I. Syafalni, K. Wakasugi, and T. Sasao, "Probe location checker for IC physical verification," 2017 IEEE TENCON, Penang, Malaysia, Nov. 5-8, 2017.

- Outstanding Contributed Paper Award, (awarded at ISMVL-2019).

- S. Nagayama, T. Sasao and J. T. Butler, "An exact optimization method using ZDDs for linear decomposition of index generation function," ISMVL-2018, May 16-18, 2018, Linz, Austria.

- Distinctive Contributed Paper Award, (awarded at ISMVL-2020).

- T. Sasao, "On a minimization of variables to represent sparse multi-valued input decision functions," *International Symposium on Multiple-Valued Logic*, (ISMVL-2019), May 21-23, 2019, Fredericton, Canada, pp. 182-187,

## VI. PEOPLE

Many people involved in the projects: J. T. Butler (visiting researcher); H. Nakahara (Prof. Tokyo Institute of Technology); S. Nagayama (Prof. Hiroshima City University); Y. Iguchi (Prof. Meiji University); A. Mishchenko (Visiting researcher); I. Syafalni (Former Ph.D. student at Kyushu Institute of Technology, now a lecturer at Bandung Institute of Technology, Indonesia)

#### REFERENCES

- [1] T. Sasao, "Four decades of multi-valued logic: Lists of highly cited papers, "International Symposium on Multiple-Valued Logic (ISMVL-2013), Toyama, Japan, May 21-24, 2013, pp. 198-202.

- [2] T. Sasao, "An application of autocorrelation functions to find linear decompositions for incompletely specified index generation functions," *International Symposium on Multiple-Valued Logic* (ISMVL-2013), Toyama, Japan, May 21-24, 2013, pp. 96-102.

- [3] S. Nagayama, T. Sasao, and J. T. Butler, "Minimization of the number of edges in an EVMDD by variable grouping for fast analysis of multistate systems," *International Symposium on Multiple-Valued Logic* (ISMVL-2013), Toyama, Japan, May 21-24, 2013, pp. 284-289.

- [4] H. Nakahara, T. Sasao and M. Matsuura, "A machine to evaluate decomposed multi-terminal multi-valued decision diagrams for characteristic functions," *International Symposium on Multiple-Valued Logic* (ISMVL-2013), Toyama, Japan, May 21-24, 2013, pp. 90-95.

- [5] T. Sasao, "Forty years of logic synthesis: Memoir," RM-2013, May 24, Toyama, Japan.

- [6] J. T. Butler and T. Sasao, "Combinational computing: One object per clock," RM-2013, May 24, Toyama, Japan.

- [7] T. Sasao, "Cyclic row-shift decompositions for incompletely specified index generation functions," IWLS-2013, Austin, Texas, June 8, 2013.

- [8] I. Syafalni and T. Sasao, "On the number of products in prefix SOPs for interval functions," *IEICE Trans. on Information and systems*, Vol. E96-D, No.5, May 2013, pp. 1086-1094.

3

- [9] H. Nakahara, T. Sasao, and M. Matsuura, "A virus scanning engine using an MPU and an IGU based on row-shift decomposition," *IEICE Transactions on Information and Systems*, Vol. E96-D, No.8, Aug. 2013, pp. 1667-1675.

- [10] H. Nakahara, T. Sasao, and M. Matsuura, "A packet classifier using LUT cascades based on EVMDDs(k)," The 23rd International Conference on Field Programmable Logic and Applications (FPL-2013), Porto, Portugal, Sept. 2-4, 2013, pp. 1-6 (CD-ROM).

- [11] H. Nakahara, T. Sasao, and M. Matsuura, "A packet classifier using parallel EVMDD(k) machine," 7th IEEE International Symposium on Embedded Multicore SoCs (MCSoC-13), Sept. 2013.

- [12] I. Syafalni and T. Sasao, "A TCAM generator for packet classification," The 31st IEEE International Conference on Computer Design (ICCD-2013), Asheville, NC, USA, Oct. 6-9, 2013, pp. 322-328.

- [13] T. Sasao, Y. Urano, and Y. Iguchi, "A heuristic method to find linear decompositions for incompletely specified index generation functions," *The 18th workshop on Synthesis and system Integration* of Mixed Information Technologies (SASIMI-2013), Sapporo, Japan, Oct. 21-22, 2013, R3-1, pp. 143-148.

- [14] I. Syafalni and T. Sasao, "A fast simplification algorithm for packet classification," The 18th workshop on Synthesis and system Integration of Mixed Information Technologies (SASIMI-2013), Sapporo, Japan, Oct. 21-22, 2013, R.5-7, pp. 328-333.

- [15] T. Sasao, "Multiple-valued index generation functions: Reduction of variables by linear transformation," *Journal of Multiple-Valued Logic* and Soft Computing, Vol. 21, No. 5-6, pp. 541-559, 2013.

- [16] S. Nagayama, T. Sasao and J. T. Butler, "EVMDD-Based analysis and diagnosis methods of multi-state systems with multi-state components," *Journal of Multiple-Valued Logic and Soft Computing*, Vol. 22, No. 1-2, pp. 59-78, 2014.

- [17] S. Nagayama, T. Sasao, and J. T. Butler, "Piecewise arithmetic expressions of numeric functions and their application to design of numeric function generators," *Journal of Multiple-Valued Logic and* Soft Computing, Vol. 23, No. 3-4, pp. 293-313, 2014.

- [18] T. Sasao, "Index generation functions: Tutorial," Journal of Multiple-Valued Logic and Soft Computing, Vol. 23, No. 3-4, pp. 235-263, 2014.

- [19] H. Nakahara, T. Sasao, M. Matsuura, "A heterogeneous multi-valued decision diagram machine for encoded characteristic function for nonzero outputs," *Journal of Multiple-Valued Logic and Soft Computing*, Vol. 23, No. 3-4, pp. 365-377, 2014.

- [20] H. Nakahara, T. Sasao and M. Matsuura, "An update method for a CAM emulator using an LUT cascade based on an EVMDD(k)," International Symposium on Multiple-Valued Logic (ISMVL-2014), Bremen, Germany, May 19-22, 2014, pp. 1-6.

- [21] T. Sasao, Y. Urano and Y. Iguchi, "A lower bound on the number of variables to represent incompletely specified index generation functions," *International Symposium on Multiple-Valued Logic* (ISMVL-2014), Bremen, Germany, May 19-22, 2014, pp. 7-12.

- [22] S. Nagayama, T. Sasao, J. T. Butler, M. A. Thornton, and T. W. Manikas, "Analysis methods of multi-state systems partially having dependent components using multiple-valued decision diagrams," *International Symposium on Multiple-Valued Logic* (ISMVL-2014), Bremen, Germany, May 19-22, 2014, pp. 190-195.

- [23] D. K. Das, D. Chowdhury, B. B. Bhattacharya and T. Sasao, "Inadmissible class of Boolean functions under stuck-at faults," *International Symposium on Multiple-Valued Logic* (ISMVL-2014), Bremen, Germany, May 19-22, 2014, pp. 237-242.

- [24] T. Sasao, "On the average number of variables to represent incompletely specified index generation function," *International Workshop on Logic and Synthesis*, (IWLS-2014), May 30-June 1, San Francisco, CA. 2014.

- [25] H. Nakahara, T. Sasao and M. Matsuura, "A packet classifier based on prefetching EVMDD(k) machines," *IEICE Transactions on Infor*mation and Systems, (Special Section on Multiple-Valued Logic and VLSI Computing) Vol. E97-D, No.9, pp. 2243-2252.

- [26] S. Nagayama, T. Sasao, J. T. Butler, M. A. Thornton, and T. W. Manikas, "On optimizations of edge-valued MDDs for fast analysis of multi-state systems," *IEICE Transactions on Information* and Systems, (Special Sections on Multiple-Valued Logic and VLSI Computing) Vol. E97-D, No. 9, pp. 2234-2242.

- [27] I. Syafalni and T. Sasao, "Head-tail expressions for interval functions," IEICE Transactions on Fundamentals of Electronics, Communication

- and Computer Sciences, Vol. E97-A, No. 10, Oct. 2014, pp. 2043-2054.

- [28] T. Sasao, Y. Urano, and Y. Iguchi, "A Method to find linear decompositions for incompletely specified index generation functions using difference matrix," *IEICE Transactions on Fundamentals of Electronics, Communication and Computer Sciences*, Vol. E97-A, No. 12, Dec. 2014, pp. 2427-2433.

- [29] J. T. Butler and T. Sasao, "High-speed hardware partition generator," ACM Transactions on Reconfigurable Technology and Systems, Vol. 7, No. 4, Dec. 2014.

- [30] T. Sasao and J. T. Butler, Applications of Zero-Suppressed Decision Diagrams, Synthesis Lectures on Digital Circuits and Systems, November 2014, 123 pages, Morgan-Claypool.

- [31] H. Nakahara, T. Sasao, M. Matsuura, H. Iwamoto, and Y. Terao, "A memory-based IPv6 lookup architecture using parallel index generation units," *IEICE Trans. Inf. and Syst.* Vol. E98-D, No. 2, pp. 262-271, Feb. 2015.

- [32] H. Nakahara, H. Yoshida, S-I. Shioya, R. Mikami, and T. Sasao, "A dynamically reconfigurable mixed analog-digital filter bank: Applied to an acoustic diagnostic system," 11th International Symposium on Applied Reconfigurable Computing(ARC-2015), April 13-17, 2015. Also, in Lecture Notes in Computer Science, Vol. 9040, 2015, pp. 267-279.

- [33] T. Sasao, "A reduction method for the number of variables to represent index generation functions: s-Min method," *International Symposium* on *Multiple-valued Logic* (ISMVL-2015), May 2015, pp. 164-169.

- [34] H. Nakahara, T. Sasao, H. Nakanishi, and K. Iwai, "An RNS FFT circuit using LUT cascades based on a modulo EVMDD," *International Symposium on Multiple-valued Logic* (ISMVL-2015), May 2015, pp. 97-102.

- [35] S. Nagayama, T. Sasao, J. T. Butler, M. Thornton, and T. Malikas, "Edge reduction for EVMDDs to speed up analysis of multi-state systems," *International Symposium on Multiple-valued Logic* (ISMVL-2015), May 2015, pp. 170-175.

- [36] T. Sasao, "On the sizes of reduced covering tables for incompletely specified index generation functions," *Reed-Muller Workshop* 2015, May 21, 2015, Waterloo, Ontario, Canada.

- [37] R. S. Stankovic, T. Sasao, and J. T. Astola, "Contributions of Yasuo Komamiya to switching theory," *Reed-Muller Workshop* 2015, May 21, 2015, Waterloo, Ontario, Canada.

- [38] I. Syafalni, T. Sasao, Xiaoqing Wen, Stefan Holst, Kohei Miyase, "Soft-error tolerant TCAM using partial don't-care keys," 20th IEEE European Test Symposium, May 25-29, 2015, Cluj-Napoca, Romania.

- [39] T. Sasao, I. Fumishi, and Y. Iguchi, "A method to minimize variables for incompletely specified index generation functions using a SAT solver," *International Workshop on Logic and Synthesis*, Mountain View, June 12-13, 2015, pp. 161-167.

- [40] I. Syafalni, T. Sasao, and X. Wen, "A soft-error tolerant TCAM for multiple-bit flips using partial don't-care keys," *International Work-shop on Logic and Synthesis*, Mountain View, June 12-13, 2015, pp. 11-18.

- [41] H. Nakahara and T. Sasao, "A deep convolutional neural network using nest residue number system," 25th International Conference on Filed-Programmable Logic and Applications (FPL2015), Sept. 2-4, 2015, London, United Kingdom, pp. 1-6.

- [42] T. Sasao, "Index generation functions: Logic synthesis for pattern matching," EPFL Workshop on Logic Synthesis and Verification, Dec. 10-11, 2015, Lausanne, Switzerland (invited).

- [43] H. Nakahara, T. Sasao, H. Iwamoto, and M. Matsuura, "LUT cascades based on edge-valued multi-valued decision diagrams: Application to packet classification," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*. Vol. 6, No.1, 2016, pp. 73-86.

- [44] H. Nakahara, T. Sasao, M. Matsuura, and H. Iwamoto, "An update method for a low power CAM emulator using an LUT cascade based on an EVMDD (k)," *Journal of Multiple-Valued Logic and Soft Computing*, Vol. 26, No. 1-2, 2016, pp. 109-123.

- [45] J. T. Butler and T. Sasao, "A set partition number system," Australasian Journal of Combinatorics, Vol. 65, No. 2, 2016, pp. 152-168,

- [46] T. Sasao, "A realization of index generation functions using multiple IGUs," *International Symposium on Multiple-valued Logic* (ISMVL-2016), May 2016, Sapporo, Japan, pp. 113-118.

- [47] H. Nakahara, T. Sasao, H. Nakanishi, K. Iwai, T. Nagao and N. Ogawa, "An FFT circuit using nested RNS in a digital spectrometer

- for a radio telescope," *International Symposium on Multiple-valued Logic* (ISMVL-2016), May 2016, pp. 60-65.

- [48] S. Nagayama, T. Sasao, and J. T. Butler, "An efficient heuristic algorithm for linear decomposition of index generation functions," *International Symposium on Multiple-valued Logic* (ISMVL-2016), May 2016, pp. 96-101.

- [49] D. Chowdhury, D. Das, B. Bhattacharya and T. Sasao, "On the inadmissible class of multiple-valued faulty functions under stuck-at faults," *International Symposium on Multiple-valued Logic* (ISMVL-2016), May 2016, pp. 276-281.

- [50] T. Sasao and J. T. Butler, "Decomposition of index generation functions using a Monte Carlo method," *International Workshop on Logic and Synthesis*, June 10-11, 2016, Austin, Texas, USA.

- [51] I. Syafalni, T. Sasao and X. Wen, "Multiple-bit-flip detection scheme for a soft-error resilient TCAM," *IEEE Computer Society Annual Symposium on VLSI*, Pittsburgh, Pennsylvania, U.S.A., July 11-13, 2016.

- [52] T. Sasao, K. Matsuura, Y. Iguchi, "A heuristic decomposition of index generation functions with many variables," SASIMI 2016, Kyoto, Oct. 24, 2016.

- [53] H. Nakahara, H. Nakanishi, K. Iwai, and T. Sasao, "An FFT Circuit for a spectrometer of a radio telescope using the nested RNS including the Constant Division," ACM SIGARCH Computer Architecture News, Vol.12. Issue 4, pp. 44-49, Jan. 2017.

- [54] T. Sasao, "A linear decomposition of index generation functions: Optimization using autocorrelation functions," *Journal of Multiple-Valued Logic and Soft Computing*, Vol. 28, No. 1, pp. 105-127, 2017.

- [55] T. Sasao, K. Matsuura, Y. Iguchi, "An algorithm to find optimum support-reducing decompositions for index generation functions." *Design Automation and Test in Europe*, (DATE-2017), March 27-31, 2017, Lausanne, Switzerland, pp.812-817.

- [56] T. Sasao, "Index generation functions: Minimization methods," *International Symposium on Multiple-valued Logic* (ISMVL-2017), Novi Sad, Serbia, May 23, 2017, pp. 197-206. (invited).

- [57] H. Nakahara, A. Jinguji, S. Sato and T. Sasao, "A random forest using a multi-valued decision diagram," *International Symposium on Multiple-valued Logic* (ISMVL-2017), Novi Sad, Serbia, May 23, 2017, ISMVL-2017, pp. 266-271.

- [58] S. Nagayama, T. Sasao and J. T. Butler, "An exact optimization algorithm for linear decomposition of index generation functions," *International Symposium on Multiple-valued Logic* (ISMVL-2017), Novi Sad, Serbia, May 23, 2017, ISMVL-2017, pp. 161-166.

- [59] T. Sasao and M. Maeta, "On affine equivalence of logic functions," International Workshop on Logic and Synthesis (IWLS-2017), Austin, Texas, June 2017.

- [60] T. Sasao, "A fast updatable implementation of index generation functions using multiple IGUs," *IEICE Trans. Inf. and Syst.* Vol. E100-D, No. 88, pp. 1574-1582, Aug. 2017.

- [61] S. Nagayama, T. Sasao, and J. T. Butler, "A balanced decision tree based heuristic for linear decomposition of index generation functions," *IEICE Trans. Inf. and Syst.* Vol. E100, No. 88, pp. 1583-1591, Aug. 2017.

- [62] I. Syafalni, K. Wakasugi, and T. Sasao, "Probe location checker for IC physical verification," 2017 IEEE TENCON, Penang, Malaysia, Nov. 5-8, 2017.

- [63] T. Sasao and J. T. Butler, "Decomposition of index generation functions using a Monte Carlo method," in Advanced Logic Synthesis, Springer, 2018, pp.209-225.

- [64] J. T. Butler and T. Sasao, "Analysis of the number of variables to represent index generation functions," in *Further Improvements in the Boolean Domain*, Cambridge Scholars Publishing, Newcastle upon Tyne, UK, 2018, pp. 25-42.

- [65] J. T. Butler and T. Sasao, "Analysis of cyclic row-shift decompositions for index generation functions," The 21st Workshop on Synthesis And System Integration of Mixed Information Technologies (SASIMI 2018), R1-14, March 27, 2018, Matsue, Japan.

- [66] T. Sasao, K. Matsuura and Y. Iguchi, "A Method to identify affine equivalence classes of logic functions," The 21st Workshop on Synthesis and System Integration of Mixed Information Technologies (SASIMI 2018), R3-18, March 27, 2018, Matsue, Japan.

- [67] I. Syafalni, K. Wakasugi, Y. Tongxin, T. Sasao and X. Wen, "Netlist conversion from costumer logic interface format (CLIF) to Verilog for legacy circuits," The 21st Workshop on Synthesis and System

- Integration of Mixed Information Technologies (SASIMI 2018), R2-17, March 28, 2018, Matsue, Japan.

- [68] J. T. Butler and T. Sasao, "An exact method to enumerate decomposition charts for index generation functions," *International Symposium on Multiple-valued Logic* (ISMVL-2018), May 16-18, 2018, Linz, Austria, pp. 138-143.

- [69] T. Sasao, "On a memory-based realization of sparse multiple-valued functions," *International Symposium on Multiple-valued Logic* (ISMVL-2018), May 16-18, 2018, Linz, Austria, pp. 50-55.

- [70] S. Nagayama, T. Sasao and J. Butler, "An exact optimization method using ZDDs for linear decomposition of index generation function," International Symposium on Multiple-valued Logic (ISMVL-2018), May 16-18, 2018, Linz, Austria. (Outstanding Contributed Paper Award), pp. 144-149.

- [71] T. Sasao, "A logic synthesis for multiple-output linear circuits," International Workshop on Logic and Synthesis (IWLS-2018), San Francisco, June 23-24, 2018.

- [72] I. Syafalni, T. Sasao, and X. Wen, "Bit-flip errors detection using random partial don't-care keys for a soft-error-tolerant TCAM," 27th International Workshop on Logic and Synthesis (IWLS-2018), San Francisco, California, June 23-24, 2018.

- [73] H. Nakahara and T. Sasao, "A high-speed low-power deep neural network on an FPGA based on the Nested RNS: Applied to an object detector," 2018 IEEE International Symposium on Circuits and Systems (ISCAS-2018), pp. 1-5, May 2018.

- [74] I. Syafalni, T. Sasao, and X. Wen, "A method to detect bit flips in a soft-error resilient TCAM," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 37, No. 6, Aug. 2018, pp. 1185-1196.

- [75] R. S. Stankovic, T. Sasao, J. T. Astola, and and A. Yamada, "Remarks on the design of first digital computer in Japan Contributions of Yasuo Komamiya," 17th International Conference on Computer Aided Systems Theory, Las Palmas de Gran Canaria, Spain, 17-22, Feb. 2019. Also in Lecture Notes in Computer Science, 12013, Springer 2020, pp.123-130.

- [76] T. Sasao, K. Matsuura, K. Kai, and Y. Iguchi, "Logic minimizers for partially defined functions," University Booth at Design, Automation and Test in Europe, (DATE 2019), Florence, Italy, March 25-28, 2019.

- [77] T. Sasao, "On a minimization of variables to represent sparse multivalued input decision functions," DATE-2019 Workshop, *Quo Vadis*, *Logic Synthesis?*, Florence, Italy, March 29, 2019.

- [78] T. Sasao, "On a minimization of variables to represent sparse multi-valued input decision functions," *International Symposium on Multiple-Valued Logic*, (ISMVL-2019), May 21-23, 2019, Fredericton, Canada, pp. 182-187, (distinctive contributed paper award).

- [79] J. T. Butler and T. Sasao, "Maximally asymmetric multiple-valued functions," *International Symposium on Multiple-Valued Logic*, (ISMVL-2019), May 21-23, 2019, Fredericton, Canada, pp. 188-193.

- [80] J. T. Butler and T. Sasao, "Realizing all index generation functions by the row-shift method," *International Symposium on Multiple-Valued Logic*, (ISMVL-2019), May 21-23, 2019, Fredericton, Canada, pp. 138-14.

- [81] S. Nagayama, T. Sasao and J. T. Butler, "A dynamic programming based method for optimum linear decomposition of index generation functions," *International Symposium on Multiple-Valued Logic*, (ISMVL-2019), May 21-23, 2019, Fredericton, Canada, pp. 144-149.

- [82] J. T. Butler and T. Sasao, "Enumerative analysis of asymmetric functions," *Reed-Muller Workshop*, (RM-2019), May 24, 2019, Fredericton, Canada.

- [83] T. Sasao, "Thirty six years of EXOR logic synthesis: Memoir," Reed-Muller Workshop, (RM-2019), May 24, 2019, Fredericton, Canada.

- [84] T. Sasao, "An improved upper bound on the number of variables to represent index generation functions using linear decompositions," 28th International Workshop on Logic and Synthesis (IWLS-2019), June 21-23, 2019, Lausanne, Switzerland.

- [85] T. Sasao, K. Matsuura, and Y. Iguchi, "On irreducible index generation functions," 28th International Workshop on Logic and Synthesis (IWLS-2019), June 21-23, 2019, Lausanne, Switzerland.

- [86] T. Sasao, Index Generation Functions, Synthesis Lectures on Digital Circuits and Systems, Morgan-Claypool, Oct. 2019, 184 pages.

- [87] T. Sasao, "On the minimization of partially defined classification functions," *International Symposium on Multiple-Valued Logic*, (ISMVL-2020), Nov. 9-11, 2020, Miyazaki, Japan, .

- [88] T. Sasao, T. Matsubara, K. Tsuji, and Y. Koga, "On a realization of universal connection networks using contact switches," *International Symposium on Multiple-Valued Logic*, (ISMVL-2020), Nov. 9-11, 2020, Miyazaki, Japan, .

- [89] T. Sasao, Y. Horikawa, and Y. Iguchi," "Handwritten digit recognition based on classification functions," *International Symposium on Multiple-Valued Logic*, (ISMVL-2020), Nov. 9-11, 2020, Miyazaki, Japan.

- [90] S. Nagayama. T. Sasao and and J. T. Butler, "On optimum linear decomposition of symmetric index generation functions," *Interna*tional Symposium on Multiple-Valued Logic, (ISMVL-2020), Nov. 9-11, 2020, Miyazaki, Japan.

- [91] J. T. Butler, T. Sasao and S. Nagayama, "Properties of multiple-valued partition functions," *International Symposium on Multiple-Valued Logic*, (ISMVL-2020), Nov. 9-11, 2020, Miyazaki, Japan.